#### **EXPERIMENT-9**

**Object:** -To study the flip-flop trainer.

#### **Resources Required:**

flip-flop trainer Kit, Patch Chord.

#### Theory:-

Basically Flip-Flops are the bistable multivibrators that stores logic 1 and logic 0.Shift registers, memory, and counters are built by using Flip – Flops. Any complex sequential machines are build using Flip – Flops. Sequential circuit (machine) output depends on the present state and input applied at that instant.

Mealy Machine is one whose output depends on both the present state and the input. Moore machines one whose output depends only on the present state of the sequential circuit. Note that the truth table of J - K Flip - Flop is same as the Master - Slave.

J – K Flip Flop and they must be remain same because IC – 7476is –ve edge trigged flip – flop and we know that race around condition is eliminated by edge triggered flip – flop. Another way of eliminating race around condition is by using Master – Slave J –K Flip – Flop. When J = K = 1 (logic HIGH), J – K Flip – Flop changes output many times for single clock pulse, it is Smaller than width of the clock pulse.

Pd < Cp = race around condition

Pd Propagation Delay

CP Clock Pulse Width

Race around condition is eliminated by using edge triggered clock pulse and using Master – Slave J - K Flip Flops.

# Implementation of J.K.Flip-Flop Design:

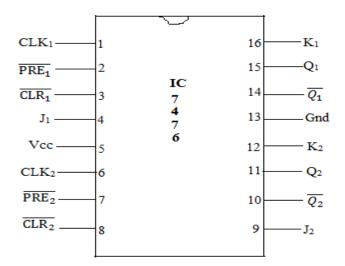

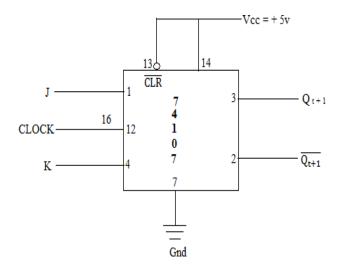

IC - 74LS76: Dual -ve edge triggered J - K Flip - Flop

## Fig Pin diagram of 7476

# **Truth Table of JK Flip – Flop:**

|   | Input |   | Output    |

|---|-------|---|-----------|

|   | S     |   | S         |

| Q | J     | K | $Q_{t+1}$ |

| 0 | 0     | 0 | 0         |

| 0 | 0     | 1 | 0         |

| 0 | 1     | 0 | 1         |

| 0 | 1     | 1 | 1         |

| 1 | 0     | 0 | 1         |

| 1 | 0     | 1 | 0         |

| 1 | 1     | 0 | 1         |

| 1 | 1     | 1 | 0         |

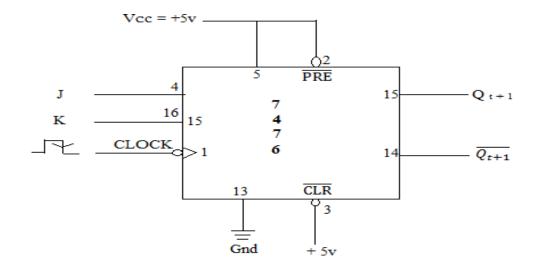

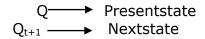

Fig J - K Flip - Flop Circuit

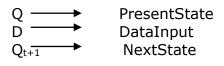

Where

$\begin{array}{ll} Q & \text{PresentState} \\ Q_{t+1} & \text{NextState} \end{array}$

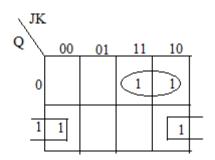

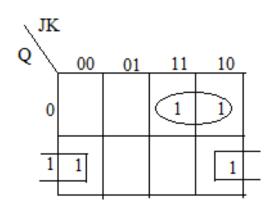

Characteristic eqn Q t + 1 = J Q + K Q

### 1. Master Slave J K Flip – Flop:

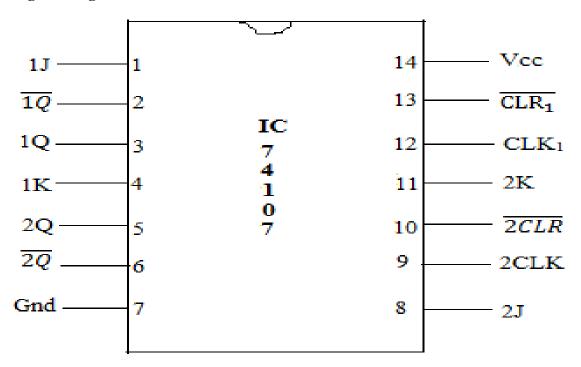

IC- 74107: Dual - Master - Slave J-K Flip - Flop

Fig Pin diagram

# **Circuit Implementation:**

Fig Master - Slave J -K Flip - Flop Circuit.

# Truth Table of Master - Slave - JK Flip - Flop:

where

|   | Input |   | Output    |

|---|-------|---|-----------|

|   | S     |   | S         |

| Q | J     | K | $Q_{t+1}$ |

| 0 | 0     | 0 | 0         |

| 0 | 0     | 1 | 0         |

| 0 | 1     | 0 | 1         |

| 0 | 1     | 1 | 1         |

| 1 | 0     | 0 | 1         |

| 1 | 0     | 1 | 0         |

| 1 | 1     | 0 | 1         |

| 1 | 1     | 1 | 0         |

Characteristic eqn $Q_{t+1}$ = JQ+KQ

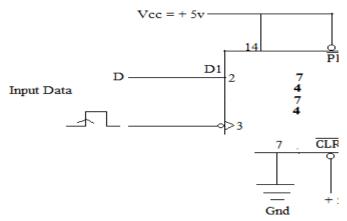

# 2. **D** – **Flip** – **Flop**:

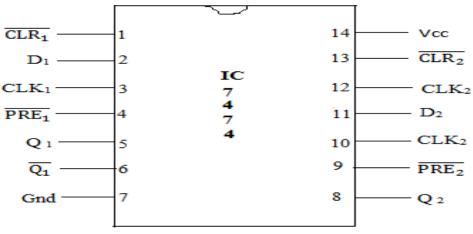

#### IC - 7474: Dual + ve edge triggered D- Flip Flop:

Fig Pin Diagram

### **Circuit Implementation:**

Fig(8.6):D-Flip-Flop

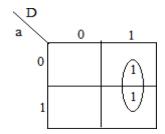

### **Truth Table of D – Flip – Flop:**

Where

|   | Input | Output    |

|---|-------|-----------|

|   | S     | s         |

| Q | J     | $Q_{t+1}$ |

| 0 | 0     | 0         |

| 0 | 1     | 1         |

| 1 | 0     | 0         |

| 1 | 1     | 1         |

|   |       |           |

$Characteristic eqn Q_{t+1} = \ D$

From Characteristic equation it is clear that next state  $Q_{t+1}$  is equal to the input data D

i.e.

$$Q_{t+1}=D$$

### **Procedure:**

- 1) Connections are made as per the circuit diagram.

- 2) Apply the -ve edge triggered, +ve edge triggered and level sensitive clock pulses as required.

- 3) Verify the truth table of all the Flip Flops.

- 4) Switch off the power supply and disconnect the circuit.

**Result:** Various Flip Flop verified